SignalTap的使用方法(2)

1、打开Quartus后,在菜单栏中,选择“Tools”->”SignalTal II Logic Analyzer”,就可以打开SignalTap工具。如下图:

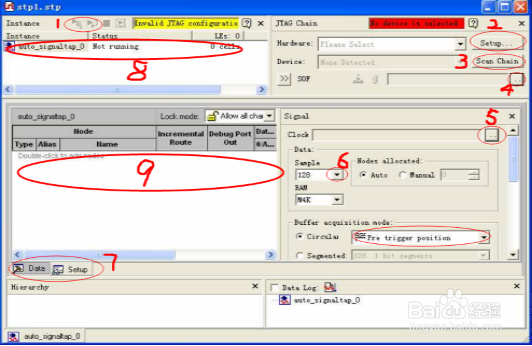

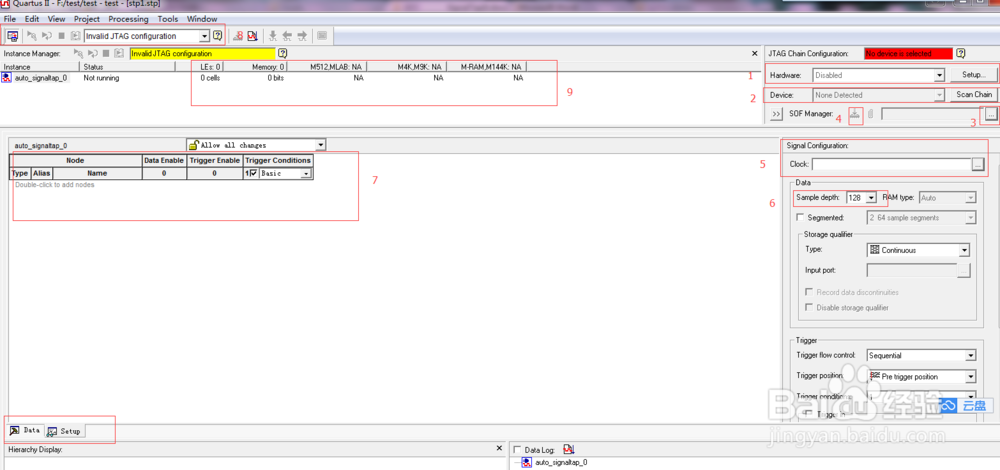

2、这是是SignalTap的界面,我们按照使用顺序简述地介绍每个部分功能。

3、红色标号1:下载线选择,点击setup选择硬件的USB接口红色标号2:硬件检测,扫描有没有FPGA硬件。红色标号3:碚枞凇悄选择工程配置文件。可以将综合后的sof文件加载进来红色标号4:正式加载sof工程文件红色标号5:设置采样时钟红色标号6:设置RAM的大小红色标号7:选择要观察的信号,并且设置触发条件红色标号8:开始运行,等待触发条件满足后显示波形红色标号9:这里可以观察FPGA资源使用情况。如果资源多于FPGA本身的资源,综合时会报错。

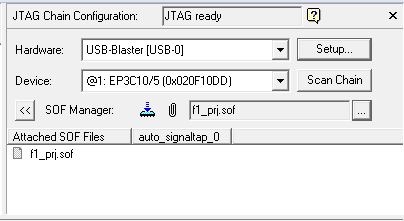

4、SignalTapII使用步骤:a、选择下载线、fpga芯片型号、工程配置文件

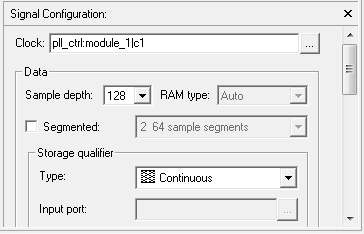

5、SignalTapII使用步骤:b、设置采样时钟、采样深度 这里我们选择内部pll的输出信号c1作为采样时钟,注意采样时钟不一定是工程里的时钟,内部任何信号都可以是采样时钟。这里我们将采样深度设置为128个。也就是我们总共能看到128采样点的数据。

6、SignalTapII使用步骤:c、选择采样信号在setup窗口中,双击空白地方,弹出如下界面 红色框是选择哪个阶段的信号,例如是综合前、综合后等,因为综合时会优化,有些信号可能就找不到了。我们一般选择pre-synthesis或Design Entry(all name)。 在Nodes Found选择我们要观察的信号,添加到右边框即可。

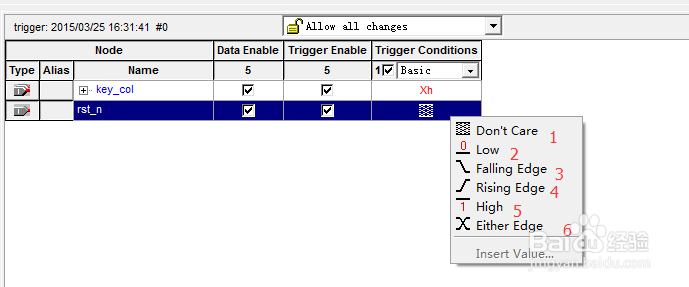

7、我们这里选择key_col和rst_n信号来观察。

8、SignalTapII使用步骤:d、设置触发条件 选择好信号后,设置殚朽羰钛触发条件。 同学们可以观察到trigger Conditions一坐逃缥卯列,key_col的值为xh,rst_n的值为don’t care。这意味着只要一观察,立刻捕获信号。 在trigger Conditions一列中,右击rst_n那个位置,将有6个选择。 don’t care:表示不关心,也就是说这个信号的值不影响触发条件。 Low :表示为0时触发,也就是说触发条件包括该信号的值为0. Falling Edge:下降沿触发。即该信号的下降沿是触发条件 Rising Edge:上升沿触发。 High:给为1时触发 Either Edge:双沿触发,即有变化时触发。以上是对一个信号的触发。

9、如果触发条件包含多个信号,如下图所示:此时的触发条件是:当rst_n为上升沿并且key_col为F。注意,这里是“与”的关系,很多同学会误认为是“或”的关系。

10、SignalTapII使用步骤:e、点击“Run Analysis”按钮,开始抓波形

11、SignalTapII使用步骤:f、观看结果 如果触发条件成立,则可在Data窗口观察到采样波形,此处是某一工程的采样结果,可以看到,其与modelsim波形是很相似的。 点击波形,则可以放大波形观看;右击波形,则是缩小波形。